Схема конвертера представлена на рисунке. Если вы начинающий радиолюбитель — не бойтесь, на самом деле схема очень простая и состоит всего из 4-х основных узлов.

Узел 1.

Это входной фильтр, ФНЧ состоит из катушек L1-L4 и конденсаторов С1-С5. Этот фильтр обязательно нужен, чтобы не перегружать ваш приёмник мощными сигналами FM-станций, сотовых телефонов, Wi-Fi роутеров и т.д.

Узел 2.

Это опорный генератор на 50МГц. Его можно запитать от отдельного USB порта компьютера или другого источника напряжением 5В.

Узел 3.

ADE, это смеситель, выполненный на высококачественной микросхеме ADE. Микросхема представляет из себя два трансформатора и диодный мост на диодах Шотки. Её параметры очень высоки и с ней получается максимальная чувствительность и динамический диапазон.

Узел4.

L7-L10, это выходной фильтр, ВФЧ, он фильтрует всё, что ниже 50МГц, то есть, чтобы ненужные продукты смесителя не поступали на вход SDR приёмника.

Все моточные данные катушек и другие данные указаны на схеме. Печатная плата конвертера не разрабатывалась, т.к. всё зависит от ваших деталей, какие сможете достать и личной фантазии при изготовлении. Конвертер можно сделать на фольгированном стеклотекстолите или даже на монтажной плате. Вот, некоторые фотки:

Настройка конвертера очень проста — установить движок резистора в нижнее по схеме положение. Затем подать питание и, вращая резистор — выставить максимальный уровень принимаемых радиосигналов. Когда будете вращать резистор, то заметите, что в один момент уровень сигналов станций расти перестал, но стал расти уровень шумов от кварцевого генератора. Вот отрегулируете резистор так, чтобы чувствительность приёмника была максимальной, а шумы от генератора минимальны.

3. Смеситель ADE 1шт http://ali.pub/1s5d37 или 5шт (с запасом, если спалите или сломаете) http://ali.pub/1s5d4d

распиновка ножек, если смотреть сверху:

Конденсаторы можно брать любые, малогаббаритные. Диодную сборку после ФНЧ, перед смесителем можно заменить на два встречно параллельных кремниевых ВЧ диода, например 1N4148 http://ali.pub/1pgho9 . Они защищают смеситель от выхода из строя от мощных радиосигналов.

Если есть желание попаять, то, можете не покупать ADE, а сделать смеситель сами, на ферритовых колечках и диодах. Так же, можете не покупать кварцевый генератор, а сделать генератор на транзисторах. Вот тут схема и описание: https://vk.com/wall-116019789_8971

А это примерное видео, такого, полностью самодельного конвертера:

работать он будет, но, конечно хуже, чем на смесителе ADE.

В заключении размещаем видео, как работает самодельный конвертер к SDR приёмнику на смесителе ADE

На стыке интересных мне областей программирования и радио зародился долгий, но интересный проект по созданию цифрового приёмника прямого преобразования, в котором аналоговых частей будет абсолютный минимум.

С каждой частью статьи я планирую дорабатывать приёмник, улучшать его характеристики, обвешивать его разными доработками, а в итоге возможно и получить полноценный трансивер.

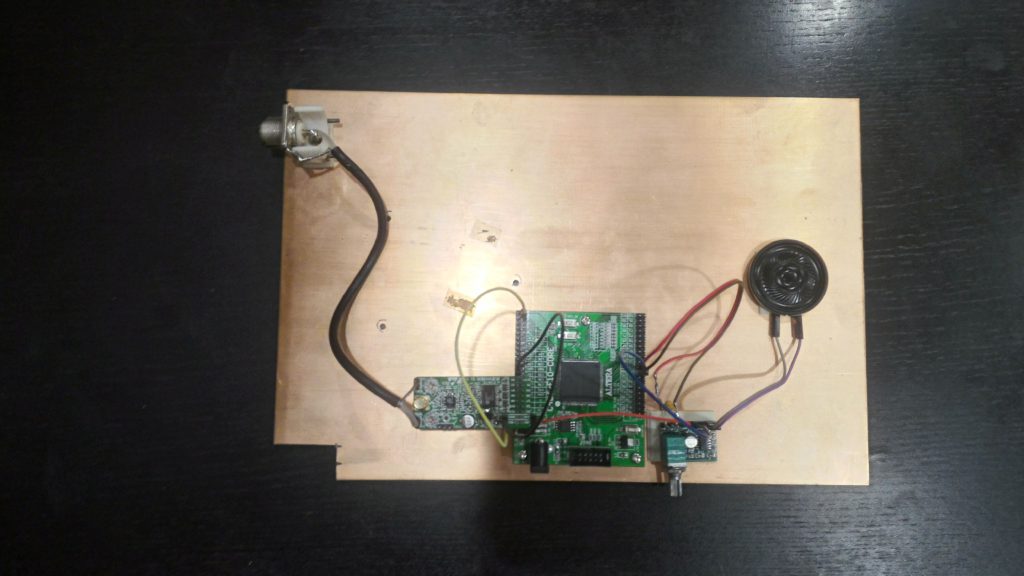

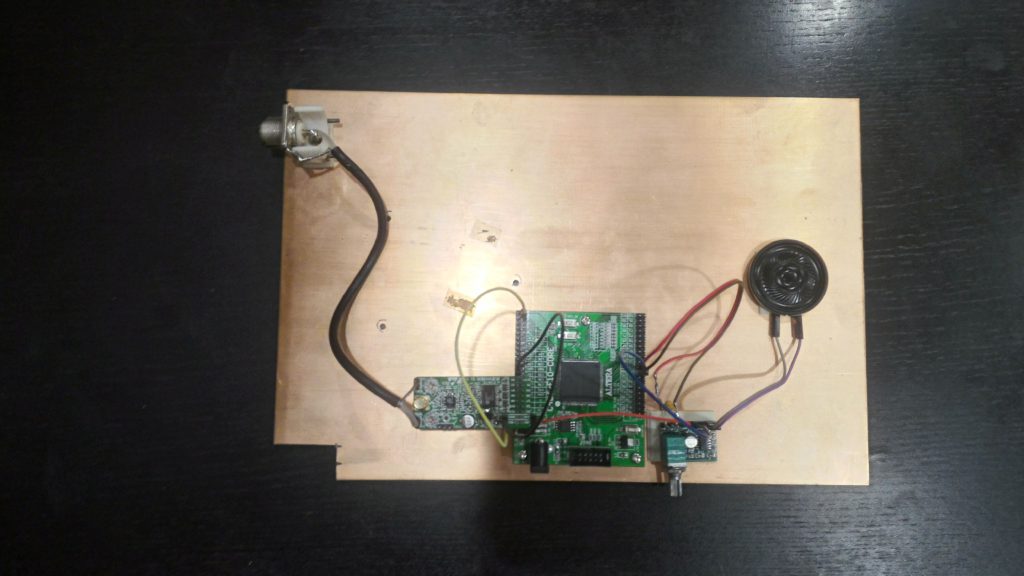

Базовый комплект будет построен на китайской АЦП AD9226.

Цифровым сердцем приёмника будет являться FPGA матрица Altera EP4CE10.

Для того, чтобы не мучатся с наушниками добавлен простейший УНЧ с питанием в 5 вольт и динамик.

Итак, соединяем все воедино (точки подключения особой роли не играют, всё настраивается и назначается программно).

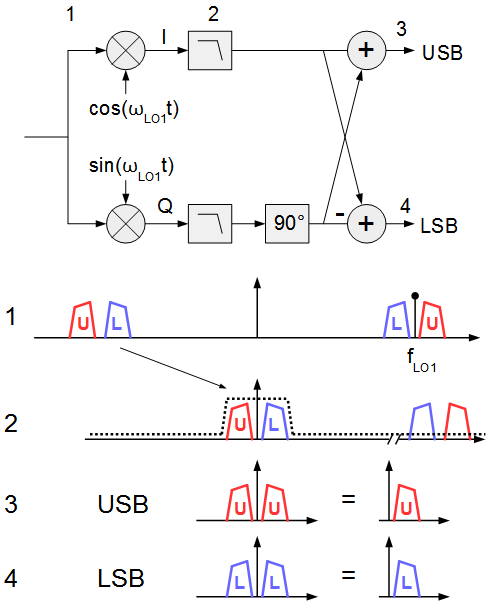

Идея приёмника заключается в смешивании оцифрованного с помощью АЦП радиосигнала с гетеродином, выдающим 2 сигнала со смещением в 90 градусов (синус и косинус).

Тем самым мы получаем комплексный сигнал (I и Q), с помощью которого достаточно легко добиться подавления зеркального канала и демодулировать полезный сигнал.

Устанавливаем среду разработки Quartus.

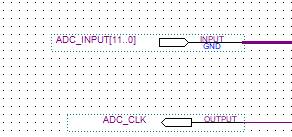

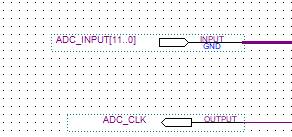

Начинаем с подключения АЦП (вход и тактовый сигнал). Т.к. внешнего кварцевого генератора нет, будем тактовать модуль силами самой FPGA (а это очень плохо в плане качества приёма, но для первой версии сгодится).

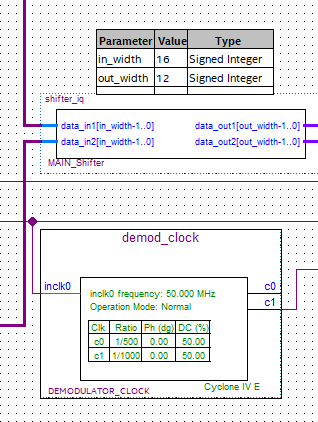

Добавляем вход кварцевого генератора планы FPGA (50 мегагерц).

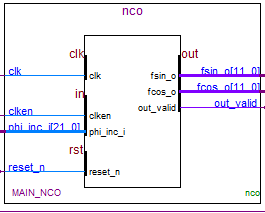

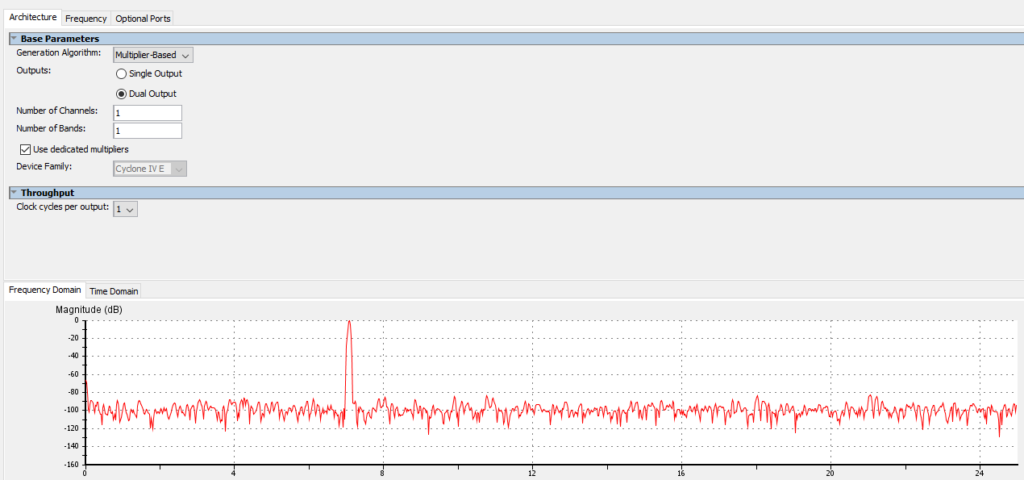

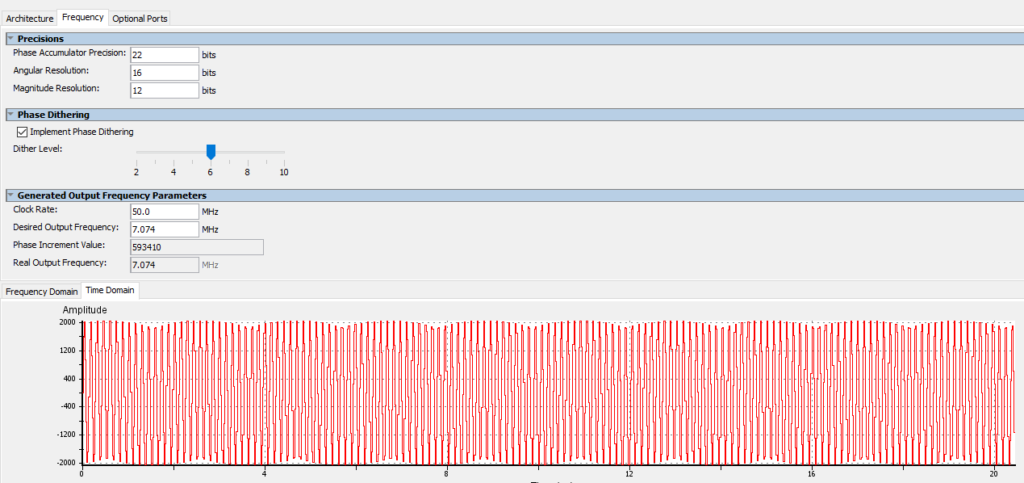

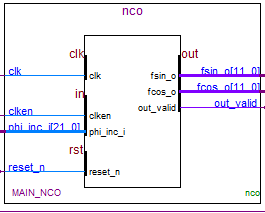

Первым делом создаём гетеродин, настроенный на частоту приёма. Его задача состоит в переносе частот с диапазона радиоволн в звуковой.

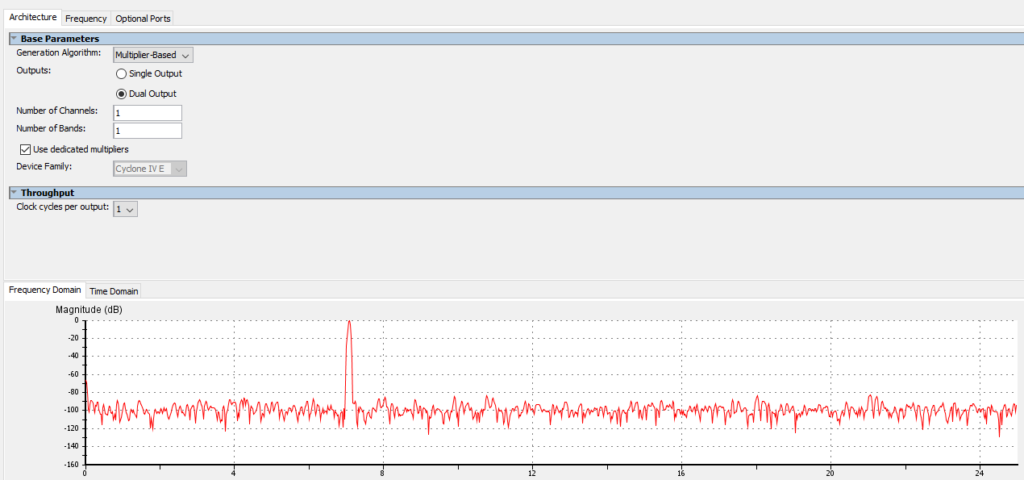

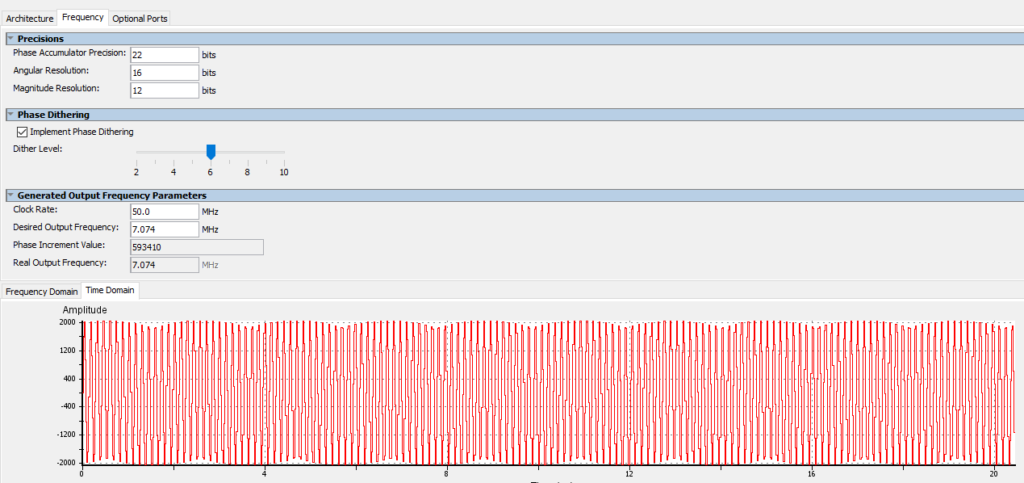

Его параметры на скриншотах:

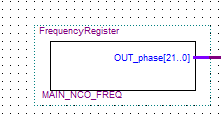

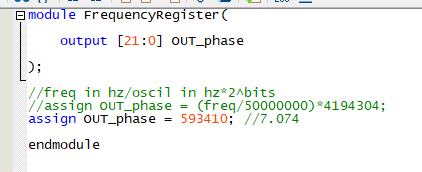

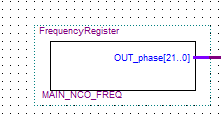

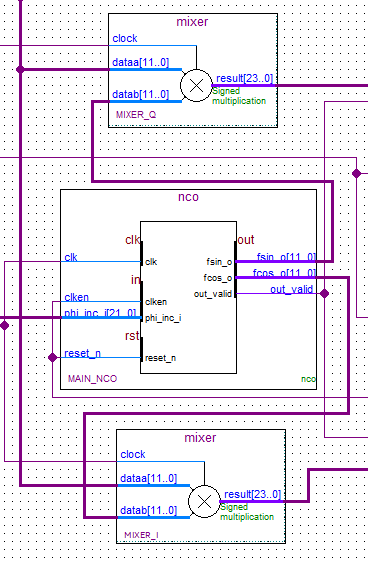

Для управления частотой гетеродина в него необходимо передать слово частоты, задающее смещение фазы, для этого подготовим отдельный модуль. Сейчас частота будет статична, но дальше планирую менять её энкодером.

Слово частоты это число, получаемое делением необходимой частоты в герцах на частоту кварцевого генератора и умноженную на двойку в степени, равной разрядности DDS-генератора (гетеродина).

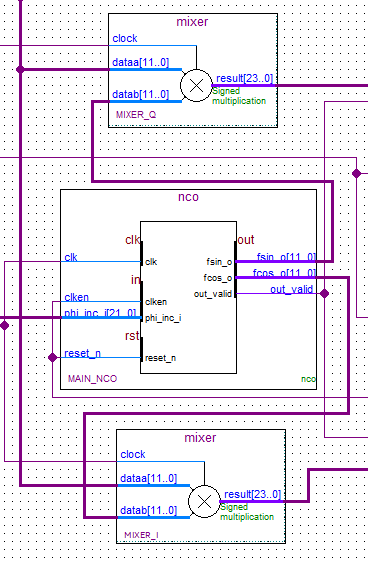

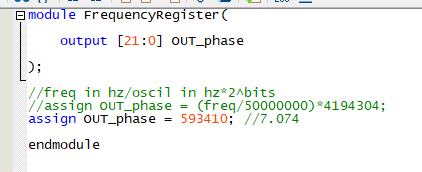

Полученный сигнал подаём на 2 смесителя (умножителя), которые обеспечивают смешивание сигнала АЦП (вход А) с сигналом гетеродина (вход B).

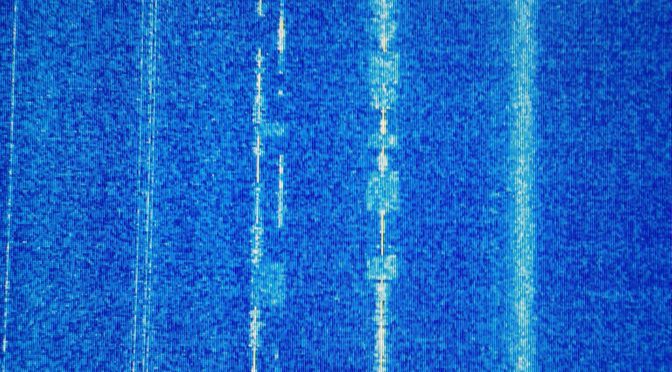

Полученный сигнал смещён на частоту гетеродина, т.е. выбранная частота теперь размещается в нулевой. А слева (да, в отрицательной части) и справа от неё находятся весь необходимый нам спектр.

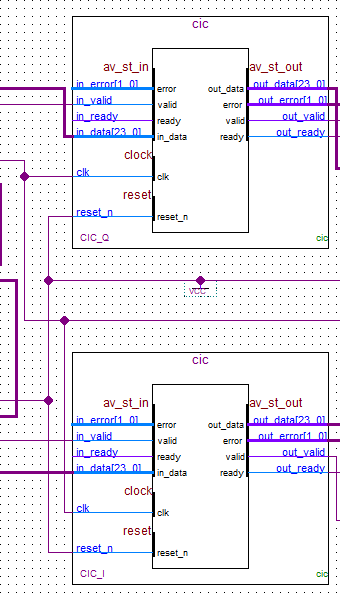

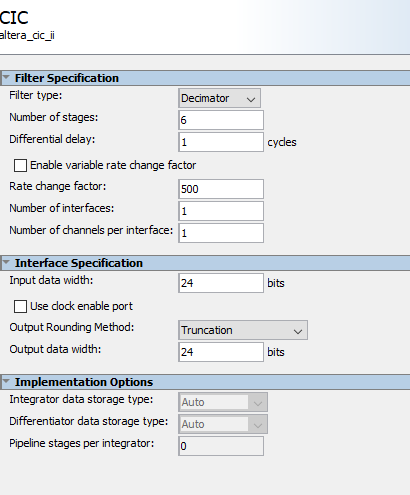

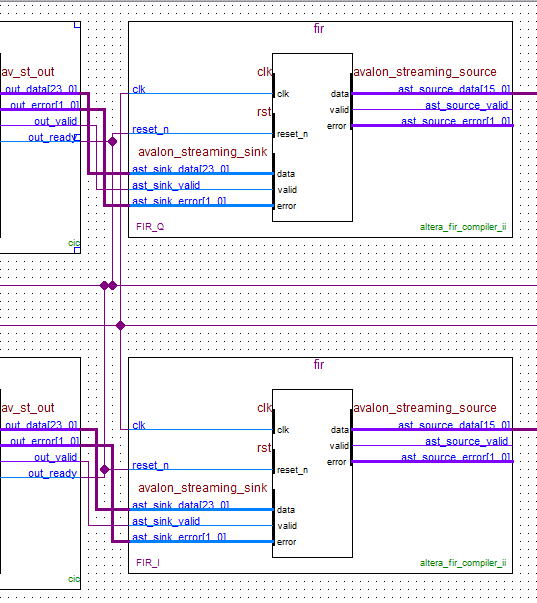

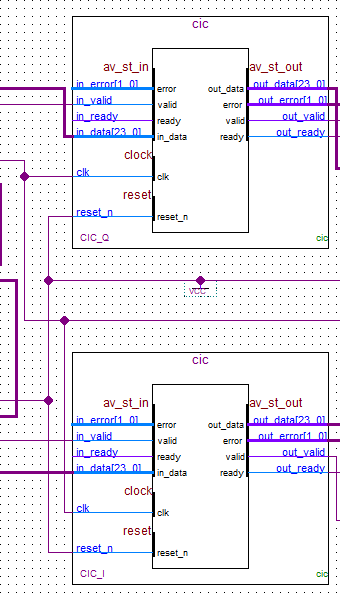

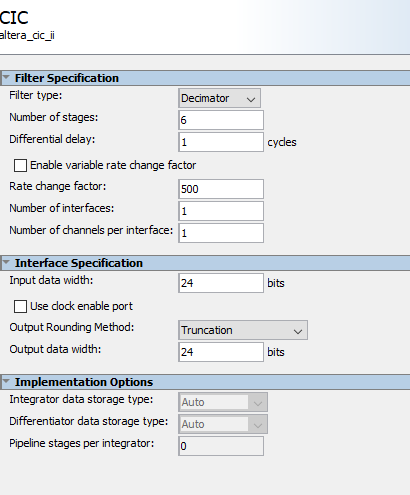

Чтобы дальше эффективно работать с сигналом, нам необходимо его децимировать (уменьшить частоту выборок), эту роль выполняет CIC фильтр.

После этого частота выборок сокращается с 50 миллионов раз в секунду до 100 000.

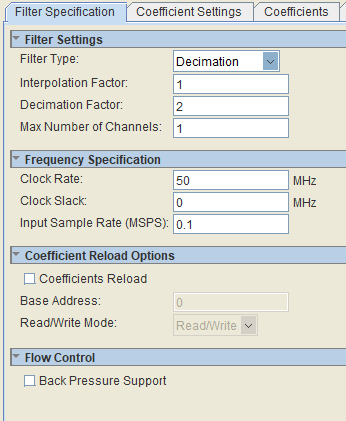

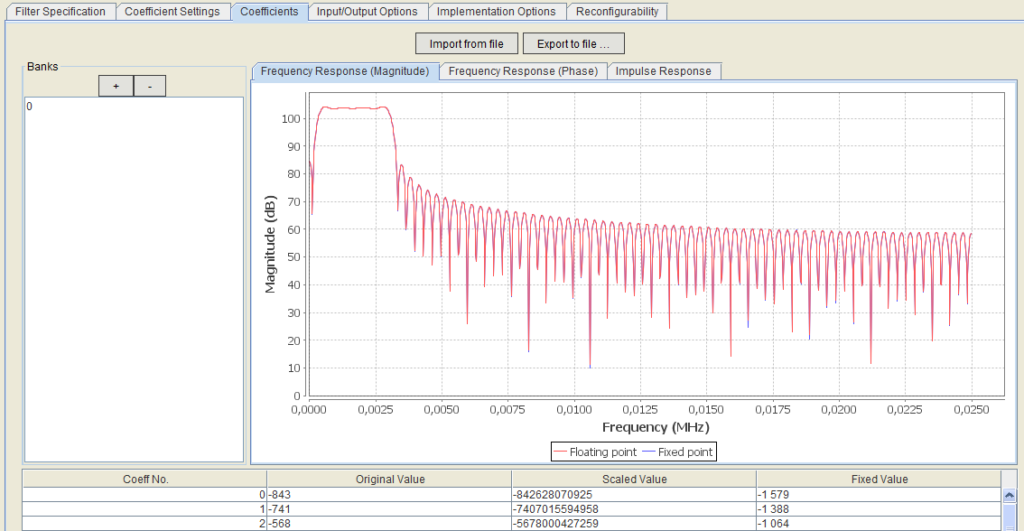

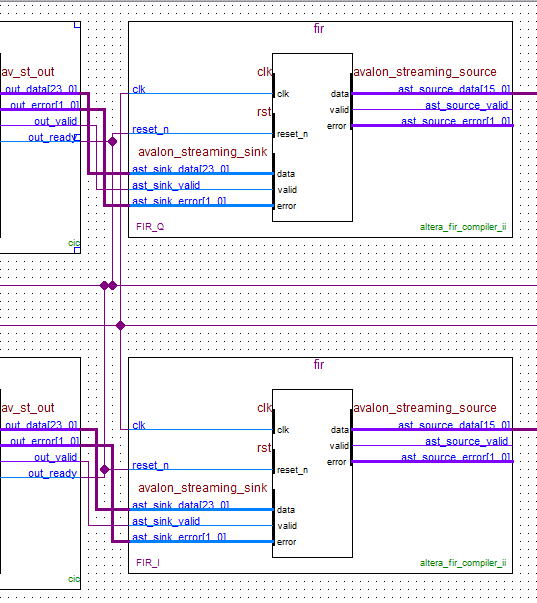

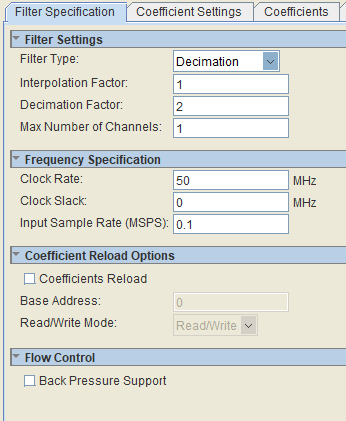

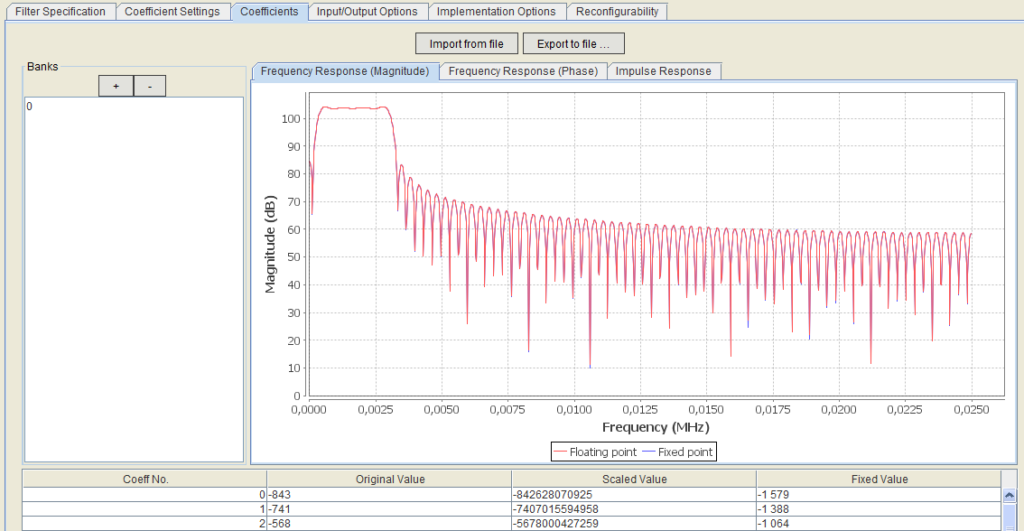

Далее нам необходимо сделать полосовой фильтр, т.к. будем принимать SSB сигнал, то фильтр полоса пропускания потребуется в районе 2700гц. Для этого воспользуемся фильтром конечных импульсных характеристик (FIR).

Для его расчёта удобно использовать следующие программы:

Iowa Hills FIR Filter Designer

WinFilter

Также, фильтр сократит число выборок с 100 000 до 50 000, что подходит для вывода на динамик.

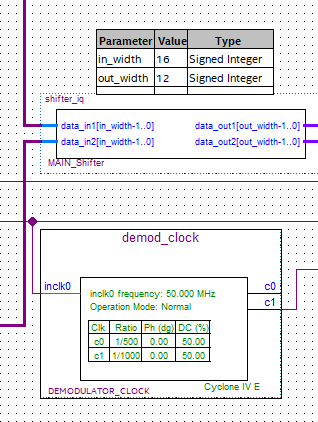

Далее сокращаем разрядность (количество бит) в потоке для дальнейшей обработки.

Ещё, потребуется PLL модуль для тактования частоты 50кгц (равной частоте дискретизации потока на текущем этапе).

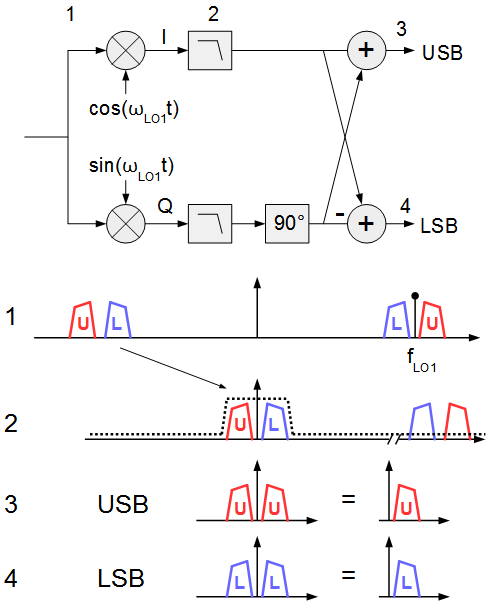

Полученные сигналы уже можно выводить на динамик, но мы не избавились от основной проблемы приёмников прямого преобразования — зеркального канала. Т.е. слушая передачи слева и справа от принимаемой частоты будем принимать их одинаково хорошо. Необходимо получить однополосный приём.

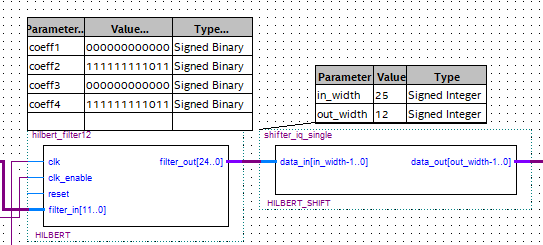

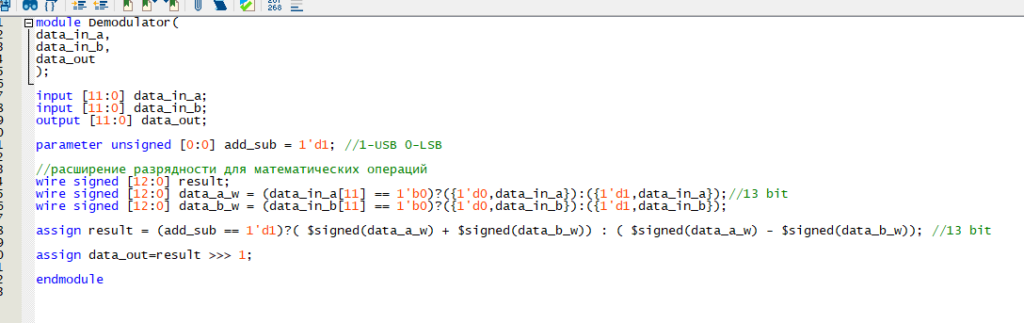

Для этого поток Q (смешанный с синусом) необходимо довернуть по фазе на 90 градусов, тем самым потоки I и Q будут относительно друг друга в 180 градусах. Их дальнейшее сложение или вычитание будет давать USB и LSB полосу приёма соответственно, подавляя всё лишнее.

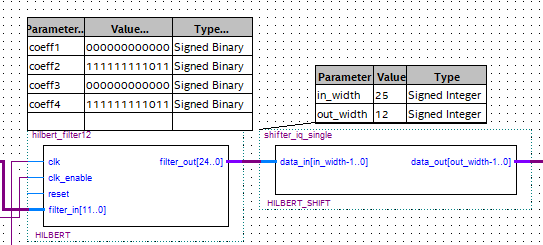

Помочь нам в этом может преобразователь (фильтр) Гильберта, рассчитанный в программе MatLab.

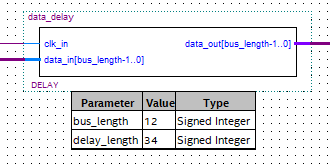

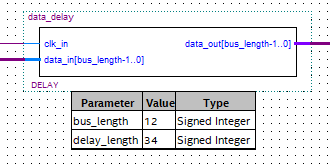

Т.к. фильтр Гильберта вызывает задержку сигнала на ((количество ступеней фильтра-1)/2) то необходимо задержать сигнал I на столько же шагов.

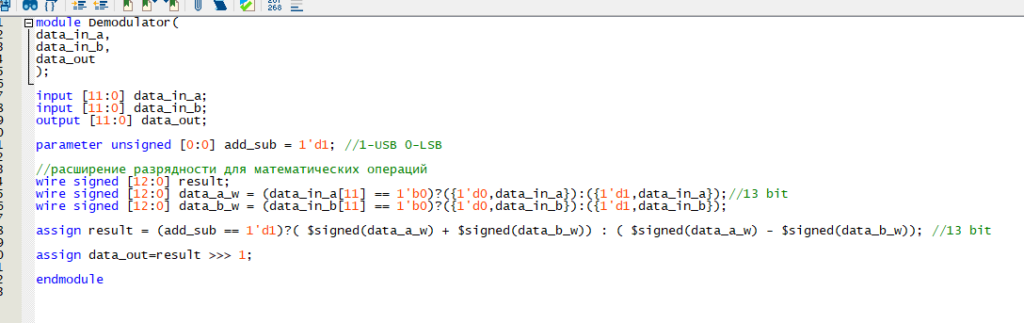

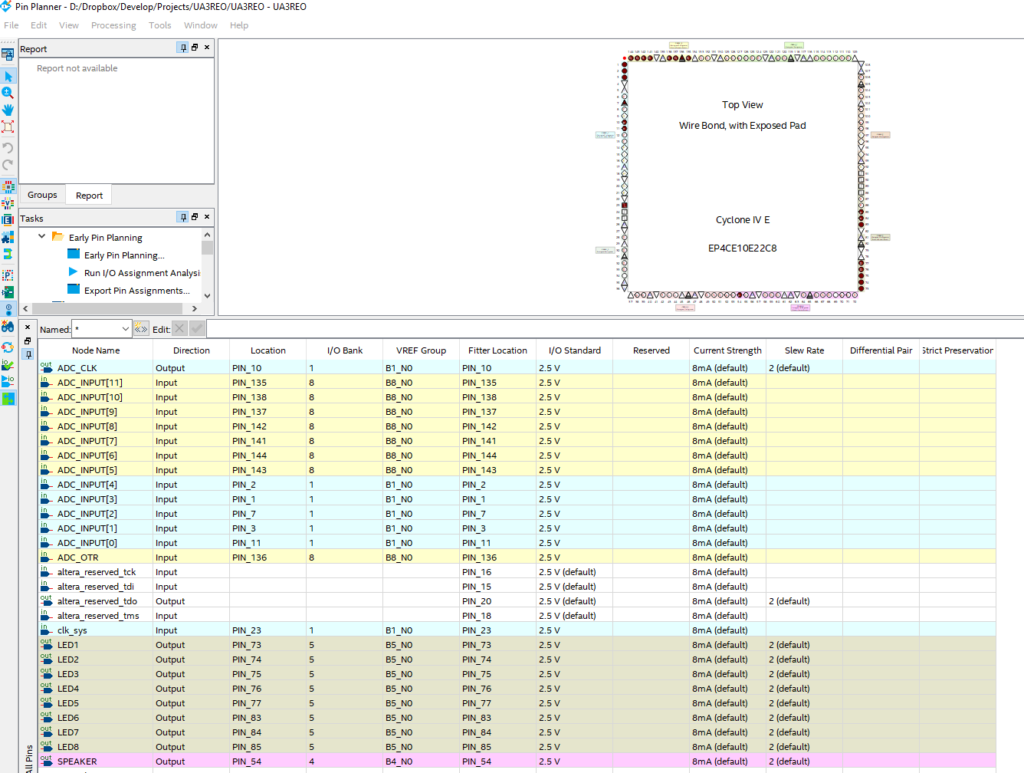

Далее мы можем сложить (или вычесть) коплексные составляющие сигнала, получив необходимую полосу приёма.

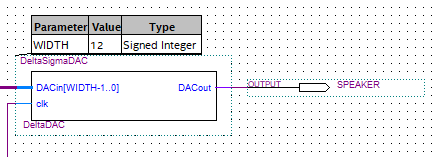

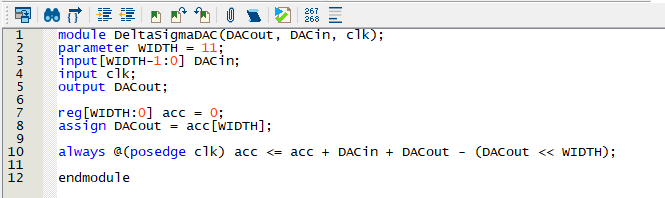

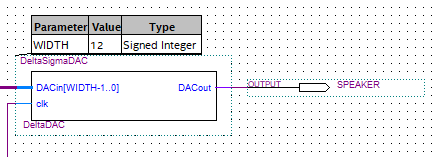

Итоговый результат подадим на дельта-сигма модулятор, смысл работы которого заключается в восстановлении синусоидального сигнала из ШИМ с помощью RC-цепочки (резистор 3.3к, конденсатор 47нф).

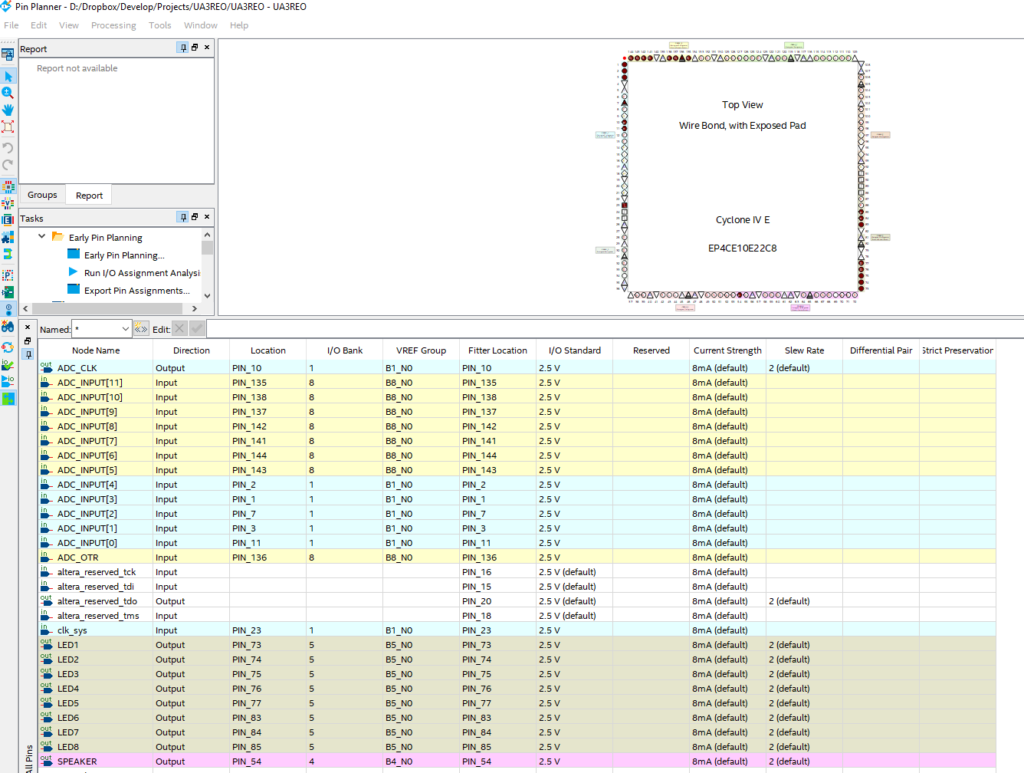

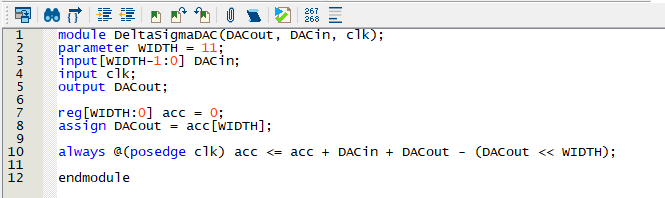

Программный код готов, можно привязать выводы в прошивке к ножкам FPGA.

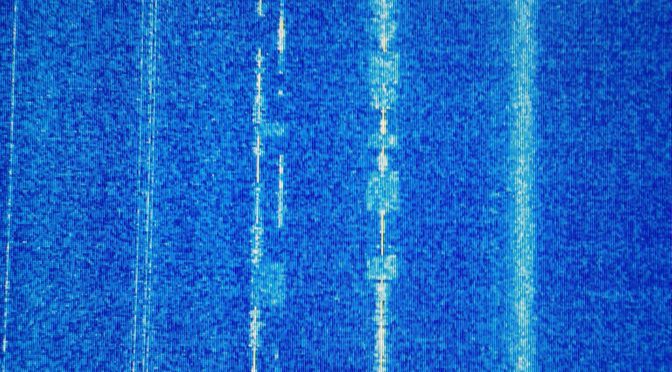

Готово, можно включить приёмник, подключить антенну ко входу АЦП и наслаждаться его работой.

Следующим шагом наверное буду делать УВЧ, управление частотой, дисплей.

При создании были использованы материалы следующих статей, без которых было бы не реально сделать хоть что-то, огромное спасибо авторам.

На стыке интересных мне областей программирования и радио зародился долгий, но интересный проект по созданию цифрового приёмника прямого преобразования, в котором аналоговых частей будет абсолютный минимум.

С каждой частью статьи я планирую дорабатывать приёмник, улучшать его характеристики, обвешивать его разными доработками, а в итоге возможно и получить полноценный трансивер.

Базовый комплект будет построен на китайской АЦП AD9226.

Цифровым сердцем приёмника будет являться FPGA матрица Altera EP4CE10.

Для того, чтобы не мучатся с наушниками добавлен простейший УНЧ с питанием в 5 вольт и динамик.

Итак, соединяем все воедино (точки подключения особой роли не играют, всё настраивается и назначается программно).

Идея приёмника заключается в смешивании оцифрованного с помощью АЦП радиосигнала с гетеродином, выдающим 2 сигнала со смещением в 90 градусов (синус и косинус).

Тем самым мы получаем комплексный сигнал (I и Q), с помощью которого достаточно легко добиться подавления зеркального канала и демодулировать полезный сигнал.

Устанавливаем среду разработки Quartus.

Начинаем с подключения АЦП (вход и тактовый сигнал). Т.к. внешнего кварцевого генератора нет, будем тактовать модуль силами самой FPGA (а это очень плохо в плане качества приёма, но для первой версии сгодится).

Добавляем вход кварцевого генератора планы FPGA (50 мегагерц).

Первым делом создаём гетеродин, настроенный на частоту приёма. Его задача состоит в переносе частот с диапазона радиоволн в звуковой.

Его параметры на скриншотах:

Для управления частотой гетеродина в него необходимо передать слово частоты, задающее смещение фазы, для этого подготовим отдельный модуль. Сейчас частота будет статична, но дальше планирую менять её энкодером.

Слово частоты это число, получаемое делением необходимой частоты в герцах на частоту кварцевого генератора и умноженную на двойку в степени, равной разрядности DDS-генератора (гетеродина).

Полученный сигнал подаём на 2 смесителя (умножителя), которые обеспечивают смешивание сигнала АЦП (вход А) с сигналом гетеродина (вход B).

Полученный сигнал смещён на частоту гетеродина, т.е. выбранная частота теперь размещается в нулевой. А слева (да, в отрицательной части) и справа от неё находятся весь необходимый нам спектр.

Чтобы дальше эффективно работать с сигналом, нам необходимо его децимировать (уменьшить частоту выборок), эту роль выполняет CIC фильтр.

После этого частота выборок сокращается с 50 миллионов раз в секунду до 100 000.

Далее нам необходимо сделать полосовой фильтр, т.к. будем принимать SSB сигнал, то фильтр полоса пропускания потребуется в районе 2700гц. Для этого воспользуемся фильтром конечных импульсных характеристик (FIR).

Для его расчёта удобно использовать следующие программы:

Iowa Hills FIR Filter Designer

WinFilter

Также, фильтр сократит число выборок с 100 000 до 50 000, что подходит для вывода на динамик.

Далее сокращаем разрядность (количество бит) в потоке для дальнейшей обработки.

Ещё, потребуется PLL модуль для тактования частоты 50кгц (равной частоте дискретизации потока на текущем этапе).

Полученные сигналы уже можно выводить на динамик, но мы не избавились от основной проблемы приёмников прямого преобразования — зеркального канала. Т.е. слушая передачи слева и справа от принимаемой частоты будем принимать их одинаково хорошо. Необходимо получить однополосный приём.

Для этого поток Q (смешанный с синусом) необходимо довернуть по фазе на 90 градусов, тем самым потоки I и Q будут относительно друг друга в 180 градусах. Их дальнейшее сложение или вычитание будет давать USB и LSB полосу приёма соответственно, подавляя всё лишнее.

Помочь нам в этом может преобразователь (фильтр) Гильберта, рассчитанный в программе MatLab.

Т.к. фильтр Гильберта вызывает задержку сигнала на ((количество ступеней фильтра-1)/2) то необходимо задержать сигнал I на столько же шагов.

Далее мы можем сложить (или вычесть) коплексные составляющие сигнала, получив необходимую полосу приёма.

Итоговый результат подадим на дельта-сигма модулятор, смысл работы которого заключается в восстановлении синусоидального сигнала из ШИМ с помощью RC-цепочки (резистор 3.3к, конденсатор 47нф).

Программный код готов, можно привязать выводы в прошивке к ножкам FPGA.

Готово, можно включить приёмник, подключить антенну ко входу АЦП и наслаждаться его работой.

Следующим шагом наверное буду делать УВЧ, управление частотой, дисплей.

При создании были использованы материалы следующих статей, без которых было бы не реально сделать хоть что-то, огромное спасибо авторам.